Можно ли увеличить разрядность алу как это сделать

Добавил пользователь Евгений Кузнецов Обновлено: 05.10.2024

Арифметико-логическое устройство (АЛУ) - центральная часть процессора, выполняющая арифметические и логические операции.

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление. ). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ. ). Операции над битами обычно подразумевают сдвиги.

Содержание

История создания

Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году он опубликовал первые научные работы по новому компьютеру, названному EDVAC (Electronic Discrete Variable Computer). Годом позже он работал со своими коллегами над разработкой компьютера для Принстонского института новейших исследований (IAS). Архитектура этого компьютера позже стала прототипом архитектур большинства последующих компьютеров. В своих работах фон Нейман указывал устройства, которые, как он считал, должны присутствовать в компьютерах. Среди этих устройств присутствовало и АЛУ. Фон Нейман отмечал, что АЛУ необходимо для компьютера, поскольку оно гарантирует, что компьютер будет способен выполнять базовые математические операции включая сложение, вычитание, умножение и деление

Структура АЛУ

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

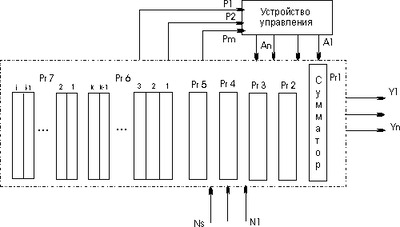

Рисунок 1 - Структурная схема арифметико-логического устройства

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация , поступающая из оперативной или пассивной памяти N1, N2, . NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма , которая записывается в виде последовательности микрокоманд A1,A2, . Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2. Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2. рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, . уs, в ОЗУ. Функции регистров, входящих в АЛУ:

- Рг1 - сумматор (или сумматоры) - основной регистр АЛУ, в котором образуется результат вычислений;

- Рг2, РгЗ - регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции);

- Рг4 - адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

- Ргб - k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 - i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся : сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

Классификация АЛУ

- По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

- По способу представления чисел различают АЛУ:

- для чисел с фиксированной точкой;

- для чисел с плавающей точкой;

- для десятичных чисел.

- По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

- По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметическо-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Операции в АЛУ

Выполняемые в АЛУ операции можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики;

- операции индексной арифметики (при модификации адресов команд);

- операции специальной арифметики;

- операции над логическими кодами (логические операции);

- операции над алфавитно-цифровыми полями.

Аннотация: Рассматриваются особенности реализации арифметико-логического устройства компьютера на примере проектирования АЛУ для умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя.

Классическая ЭВМ состоит из трех основных устройств: арифметико-логического устройства , устройства управления и запоминающего устройства. Рассмотрим особенности организации этих устройств. Прежде всего, рассмотрим структуру арифметико-логического устройства .

В современных ЭВМ арифметико-логическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер . Однако знание структуры и принципов работы АЛУ весьма важно для понимания работы компьютера в целом. Для лучшего понимания этих вопросов проведем синтез арифметического устройства, предназначенного для выполнения только одной операции – умножения чисел с фиксированной запятой , заданных в прямом коде, со старших разрядов множителя [13] . В ходе этого процесса также обратим внимание на особенности использования рассмотренных выше основных схемотехнических элементов ЭВМ.

Синтез АЛУ проходит в несколько этапов. Сначала необходимо выбрать метод, по которому предполагается выполнение операции , и составить алгоритм соответствующих действий. Исходя из алгоритма и формата исходных данных, следует определить набор составляющих АЛУ элементов. Затем требуется определить связи между элементами, установить порядок функционирования устройства и временную диаграмму управляющих сигналов, которые должны быть поданы на АЛУ от устройства управления.

Пусть операнды имеют вид:

где x0 , y0 – знаковые разряды.

Операция умножения чисел с фиксированной запятой , заданных в прямом коде, со старших разрядов множителя выполняется по следующей формуле:

![[X]_</p>

<p>= 0.1101; Sign X = 0 \\ [Y]_ = 1.1011; Sign Y = 1 \\ Sign Z = 0 \oplus 1 = 1 \\ |X| = 0. 1 1 0 1 \\ |Y| = 0. 1 0 1 1 \\ y_y_y_y_ \\ +0.00000000 |Z| = 0 \\ y_ = 1 0.01101000 1 \cdot |X| \cdot 2^ \\ + \ovwerline |Z| = |Z| + |X| \cdot 2^ \\ y_ = 0 0.00000000 0 \cdot |X| \cdot 2^ \\ + \overline |Z| = |Z| + 0 \\ y_ = 1 0.00011010 1 \cdot |X| \cdot 2^ \\ + \overline |Z| = |Z| + |X| \cdot 2^ \\ y_ = 1 0.00001101 1 \cdot |X| \cdot 2^ \\ \overline |Z| = |Z| + |X| \cdot 2^](https://intuit.ru/sites/default/files/tex_cache/7af37921efed33c4bbe7f79df3e492e3.jpg)

Алгоритм вычислений представлен на рис. 3.1

Рис. 3.1. Алгоритм операции умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя

Каждой переменной, представленной в алгоритме, в схеме должен соответствовать элемент хранения. Разрядность модуля произведения равна сумме разрядностей сомножителей. Умножение двоичного числа на 2 -i обеспечивается сдвигом этого числа вправо на соответствующее количество разрядов. Переход к анализу очередного разряда множителя ( i = i + 1 ) может быть обеспечен сдвигом регистра множителя на один разряд в сторону старших разрядов.

Исходя из этого, определим состав оборудования, необходимого для реализации АЛУ заданного типа для n = 4 ( таблица 3.1).

АЛУ предназначено для выполнения арифметических и логических операций с двоичными числами заданной разрядности в зависимости от кодов, подаваемых на управляющие входы АЛУ.

Известны следующие разновидности АЛУ: комбинационного типа, с магистральной структурой, на основе блоков памяти. В соответствии с типами данных различают АЛУ с фиксированной точкой, АЛУ с плавающей точкой, десятичное, а по принципам построения АЛУ бывают с микропрограммным уровнем управления и на жесткой логике.

В типовой состав АЛУ входят сумматоры, которые непосредственно выполняют элементарные операции, регистры для хранения операндов и результатов, сдвиговые регистры, логические схемы И, ИЛИ, НЕ, схемы для преобразования прямого кода числа в дополнительную форму, а также АЛУ может включать дополнительные схемы аппаратного умножения и деления для целочисленных операндов. АЛУ является базовым узлом микроконтроллеров, микропроцессоров, сигнальных процессоров и др. вычислительных устройств и работает в сочетании с ОЗУ, регистрами сдвига, регистрами общего назначения и др. АЛУ строится на основе разным типов логик, в основном отвечающим критериям высокого быстродействия.

Примером АЛУ ТТЛ-логики может служить микросхема К155ИПЗ, в КМОП-логике — микросхема 564ИПЗ. Аналогом микросхемы К155ИПЗ в программе Multisim является микросхема 74181, представляющая собой четырехразрядное АЛУ, предназначенное для работы с двумя четырехразрядными числами: А = А3А2А1А0 и В = В3В2В]В0, а в качестве управляющих входов используется 4-разрядное кодовое слово S = S3S2SiS0, определяющее функцию выбора режима и одноразрядный вход контроля режима М; кроме того, одноразрядный вход переноса CN также расширяет возможности контроля режима для выполнения арифметических операций, что показано в табл. 3.5.

На выходах F3F2F]Fo выдаются результаты всех выполняемых действий. На выходе CN4 образуется сигнал переноса, а на выходе AEQB формируется уровень логической единицы при равенстве входных чисел, позволяющий определить соотношения неравенства между числами А и В с использованием сигнала на выходе CN4, как показано в табл. 3.6.

Назначение АЛУ.

Арифметическо–логические устройства предназначены для выполнения арифметических и логических операций над

–разрядными операндами А =

Вид выполняемой операции задается:

— режим), позволяющим выбрать арифметическую (М = 0) или логическую (

● 4–разрядным кодом Е3Е2Е1Е0, позволяющим выбрать одну из 16 арифметических и 16 логических операций. Логические операции над операндами

Помимо операндов на вход АЛУ подается сигнал переноса С0. Результат выполнения операции снимается с выходов в виде функций

=0,1,2,3) для отдельных разрядов.

Рассмотрим особенности АЛУ на примере 4–разрядных устройств. Основой для построения АЛУ служат СУММАТОРЫ с ускоренным переносом.

Принцип построения сумматоров.

В многоразрядных сумматорах для сложения отдельных разрядов (начиная с младшего) двоичных чисел используются полные одноразрядные сумматоры. На входы сумматора поступают сигналы

, 1–го разряда и сигнал С

переноса из предыдущего разряда, а с выхода снимаются сигналы текущего разряда

суммы и переноса

в следующий разряд.

Правила функционирования полного сумматора отображены в табл. 4.2.1.

Воспользовавшись табл. 4.2.1 и картой Карно (рис. 4.2.1) составим выражения для суммы и выходного сигнала переноса:

обозначены операции сложения по модулю два и логического сложения.

Из (4.2.2) следует, что:

= 1 вырабатывается (генерируется) при наличии обоих сигналов в данном разряде (т.е. перенос происходит при А

= 1), поэтому он называется функцией генерации переноса;

= 1 разрешает прохождение переноса С

= 1 на выход, поэтому он называется функцией распространения переноса. Используя (4.2.2), запишем следующие выражения для сигналов переноса:

Выражения (4.2.3), (4.2.4) свидетельствуют о том, что для получения сигналов переноса С

= 0, 1, 2, 3) достаточно располагать функциями

(по сути, входными сигналами

разрядов слагаемых) и сигналом внешнего переноса С0. Они описывают двухступенчатые комбинационные устройства, в первой ступени которых формируются логические произведения, а во второй — логические суммы. Поэтому можно считать, что сигналы всех переносов будут сформированы одновременно и за более короткий промежуток времени, чем в схеме многоразрядного сумматора с последовательным переносом.

Рассмотренный способ формирования переносов часто называется параллельным,

а сумматоры, построенные по этому способу, — сумматорами с параллельным переносом.

Используя соотношения (4.2.3), (4.2.4), можно построить схему ускоренного (параллельного) переноса для 4–разрядного сумматора (рис. 4.2.2). Как видно из рис. 4.2.2, схема ускоренного переноса с помощью входных сигналов С0,

0, 1, 2, 3) формирует переносы в старшие разряды С1…С4, а также функции генерации

переносов, используемые при групповом включении 4–разрядных сумматоров.

Отметим, что на основе 4–разрядных сумматоров можно построить сумматоры с разрядностью 8, 12, 16 и т. д. с параллельным групповым переносом.

Для выполнения логических операций и расширения функциональных возможностей рассмотренного выше сумматора примем следующие меры:

Читайте также: